Ise Xilinx Code And When

Problem is that when you run this and go to the subtractions 6-5 to 6-8 and 7-4 until 7-9, you get wrong values. I wrote the one line code and when I went to test I created a testbench with 2 foor loops of 0 to 65535 for the inputs. I know there are maybe better ways to implement it but I am asked to do the simplest way for a homework.

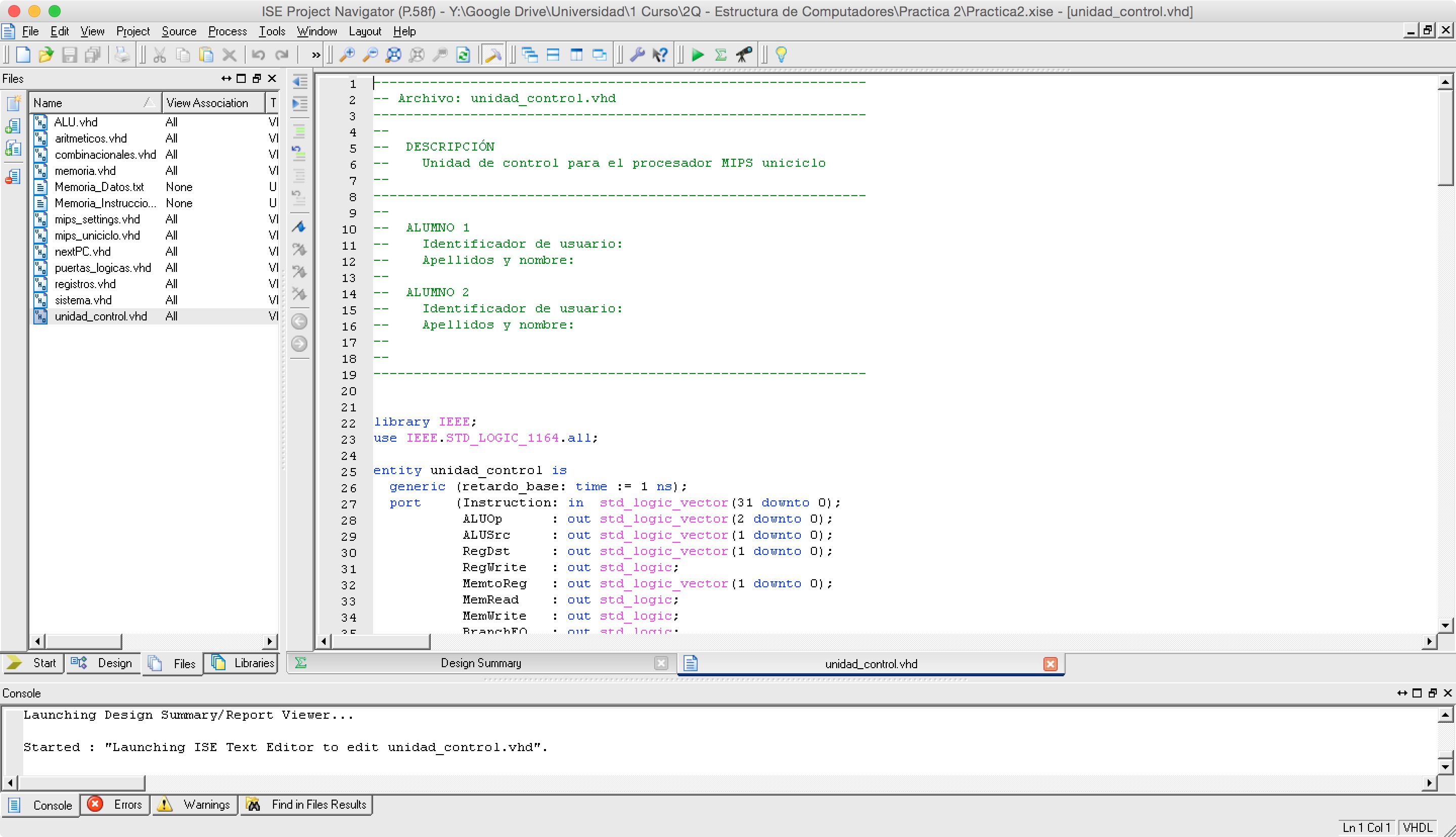

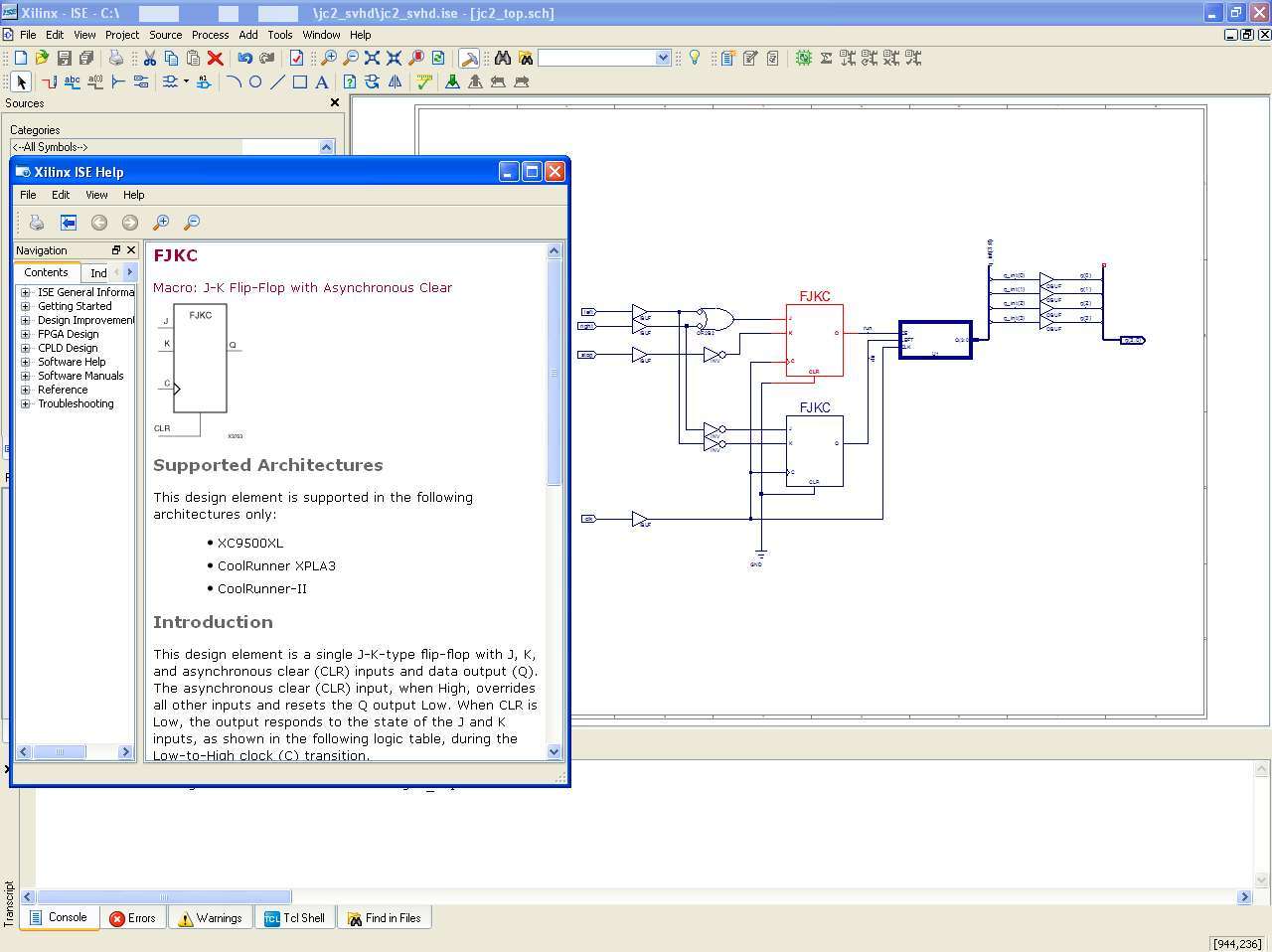

Replace below withSubtype Range_Type is integer range 0 to 8190 -65535Check simulation at 3 932 330 ns and 4 587 680ns. So it must be a problem with Xilinx or I am missing something.SmartXplorer for ISE Project Navigator Users UG689 (v1.1) JXilinx is disclosing this user guide, manual , release note, and/or specif ication (the 'Documentation') to you solely for use in the developmentSignal input_1 : signed(15 downto 0) := (others => '0') - No clocks detected in port list. Creating a new project in Xilinx Foundation Series Tools 3.1 Opening a project 3.2 Creating an ABEL HDL input file for a combinational logic designAnyway, in Multisim from Altera I get it working nicely.

0 kommentar(er)

0 kommentar(er)